编辑:Helen 发布:2018-11-12 11:15

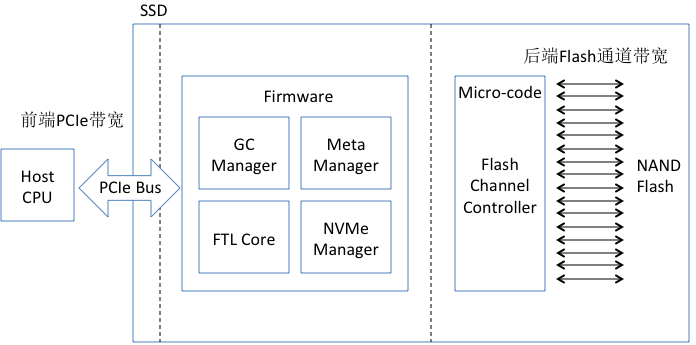

NVMe SSD 厂商Spec给出的性能非常完美,前面也给出了NVMe SSD和磁盘之间的性能对比,NVMe SSD的性能的确比磁盘高很多。但在实际应用过程中,NVMe SSD的性能可能没有想象中的那么好,并且看上去不是特别的稳定,找不到完美的规律。和磁盘介质相比,SSD的性能和很多因素相关,分析SSD的性能影响因素,首先需要大体了解SSD构成的主要部分。主要包括主机CPU、PCIe互连带宽、SSD控制器及FTL软件、后端NAND Flash带宽、NAND Flash介质。影响SSD性能的主要可以分成硬件、软件、客观三大因素。

1、硬件因素

a)NAND Flash本身。不同类型的NAND Flash本身具有不同的性能,例如SLC的性能高于MLC,MLC的性能优于TLC。选择不同的工艺、不同类别的NAND Flash,都会具有不同的性能。

b)后端通道数(CE数量)及总线频率。后端通道数决定了并发NAND Flash的数量,决定了并发能力。不同的SSD控制器支持不同数量的通道数,也决定了SSD的后端吞吐带宽能力。NAND Flash Channel的总线频率也决定了访问Flash的性能。

c)SSD控制器的处理能力。SSD控制器中会运行复杂的FTL(Flash Translation Layer)处理逻辑,将逻辑块读写映射转换成NAND Flash 读写请求。在大数据块读写时,对处理器能力要求不是很高;在小数据块读写时,对处理器能力要求极高,处理器能力很容易成为整个IO系统的性能瓶颈点。

d)SSD控制器架构。通常SSD控制器采用SMP或者MPP两种架构,早期的控制器通常采用MPP架构,多个小处理器通过内部高速总线进行互连,通过硬件消息队列进行通信。内存资源作为独立的外设供所有的处理器进行共享。这种架构和基于消息通信的分布式系统类似。MPP架构的很大优势在于性能,但是编程复杂度较高;SMP架构的性能可扩展性取决于软件,编程简单,和在x86平台上编程相似。不同的控制器架构会影响到SSD的总体性能,在SSD设计时,会根据设计目标,选择不同类型的SSD控制器。

e)内存支持容量。为了追求高性能,SSD内部的映射资源表会常驻内存,映射表的内存占用大小是盘容量的0.1%,当内存容量不够大时,会出现映射表换入换出的问题,影响到性能。

f)PCIe的吞吐带宽能力。PCIe前端带宽体现了SSD的前端吞吐能力,目前NVMe SSD采用x4 lane的接入方式,上限带宽为3GB/s,当后端NAND Flash带宽和处理器能力足够时,前端PCIe往往会成为性能瓶颈点。NAND Flash具有很高的读性能,目前来看,SSD的读性能在很大程度上受限于PCIe总线,因此需要快速推进PCIe4.0标准。

g)温度对性能造成影响。在NAND Flash全速运行的情况下,会产生较大的散热功耗,当温度高到一定程度时,系统将会处于不正常的工作状态,为此,SSD内部做了控温系统,通过温度检测系统来调整SSD性能,从而保证系统温度维持在阈值之内。调整温度会牺牲性能,本质上就是通过降低SSD性能来降温。因此,当环境温度过高时,会影响到SSD的性能,触发SSD内部的温度控制系统,调节SSD的性能。

h)使用寿命对性能造成影响。NAND Flash在不断擦除使用时,Flash的bit error会不断上升,错误率的提升会影响到SSD的IO性能。

2、软件因素

a)数据布局方式。数据布局方法需要充分考虑NAND Flash中的并发单元,如何将IO操作转换成NAND Flash的并发操作,这是数据布局需要考虑的问题。例如,采用数据交错的方式在多通道page上进行数据布局,通过这种方式可以优化顺序带宽。

b)垃圾回收/wear leveling调度方法。数据回收、wear leveling、data retention等操作会产生大量的NAND Flash后端流量,后端流量直接反应了SSD的写放大系数,也直接体现在后端带宽的占用。垃圾回收等产生的流量也可以称之为背景流量,背景流量会直接影响到前端用户性能。因此需要对背景流量和用户流量之间进行合理调度,使得用户IO性能达到最佳。

c)OP预留。为了解决坏块、垃圾回收等问题,在SSD内部预留了一部分空闲资源,这些资源被称之为OP(Overprovisioning)。OP越大,GC过程中平均搬移的数据会越少,背景流量会越小,因此,写放大降低,用户IO性能提升。反之,OP越小,性能会越低,写放大会越大。在SSD容量较小的时代,为了提升SSD的使用寿命,往往OP都设置的比较大。

d)Bit error处理影响性能。在SSD内部采用多种机制来处理NAND Flash所产生的Bit error。ECC纠错、read retry、soft LDPC以及RAIN都是用来纠正bit翻转导致的错误。当Bit错误率增加时,软件处理的开销越大,在bit控制在一定范围之内,完全可以通过硬件进行纠正。一旦软件参与到bit纠正的时候,会引入较大的性能开销。

e)FTL算法。FTL算法会影响到SSD性能,对于不同用途的SSD,FTL的设计与实现是完全不同的,企业级SSD为了追求高性能,通常采用Flat mapping的方式,采用大内存缓存映射表;消费级SSD为了追求低成本,通常采用元数据换入换出的方式,并且采用SLC+TLC的组合方式进行分层存储,也可以采用主机端内存缓存元数据信息,但是这些方式都会影响到性能。

f)IO调度算法。NAND Flash具有严重的性能不对称性,Flash Erase和Program具有ms级延迟,Flash read的延迟在us级。因此,如何调度Erase、Program以及read是SSD后端设计需要考虑的问题。另外,前端IO以及背景IO之间的调度也是需要权衡考虑,通过IO调度可以达到最佳性能表现。在IO调度过程中,还需要利用NAND Flash的特性,例如Program Suspension,通过这些特性的利用,最优化SSD前端IO性能。

g)驱动软件。驱动软件运行在主机端,通常分为内核态和用户态两大类,内核态驱动会消耗较多的CPU资源,存在频繁上下文切换、中断处理,因此性能较低;用户态驱动通常采用Polling IO处理模式,去除了上下文切换,可以充分提升CPU效率,提升整体IO性能。

h)IO Pattern对性能产生影响。IO Pattern影响了SSD内部的GC数据布局,间接影响了GC过程中的数据搬移量,决定了后端流量。当IO Pattern为全顺序时,这种Pattern对SSD内部GC是最为友好的,写放大接近于1,因此具有最好的性能;当IO Pattern为小块随机时,会产生较多的GC搬移数据量,因此性能大为下降。在实际应用中,需要通过本地文件系统最优化IO Pattern,获取最佳性能。

3、客观因素

a)使用时间越长会导致SSD性能变差。使用时间变长之后,SSD内部NAND Flash的磨损会加重,NAND Flash磨损变大之后会导致bit错误率提升。在SSD内部存在一套完整的bit错误恢复机制,由硬件和软件两大部分构成。当bit错误率达到一定程度之后,硬件机制将会失效。硬件机制失效之后,需要通过软件(Firmware)的方式恢复翻转的bit,软件恢复将会带来较大的延迟开销,因此会影响到SSD对外表现的性能。在有些情况下,如果一块SSD在掉电情况下放置一段时间之后,也可能会导致性能变差,原因在于SSD内部NAND Flash中存储电荷的漏电,放置一段时间之后导致bit错误率增加,从而影响性能。SSD的性能和时间相关,本质上还是与NAND Flash的比特错误率相关。

b)环境温度也会对性能造成影响。为了控制SSD温度不能超过上限值,在SSD内部设计有一套温度负反馈机制,该机制通过检测的温度对NAND Flash后端带宽进行控制,达到降低温度的效果。如果一旦温度负反馈机制开始工作,那么NAND Flash后端带宽将会受到限制,从而影响前端应用IO的性能。

| 存储原厂 |

| 三星电子 | 55700 | KRW | 0.00% |

| SK海力士 | 184400 | KRW | +3.42% |

| 铠侠 | 1870 | JPY | +3.14% |

| 美光科技 | 79.780 | USD | +3.05% |

| 西部数据 | 40.780 | USD | +1.52% |

| 闪迪 | 32.850 | USD | +1.73% |

| 南亚科 | 37.00 | TWD | -1.07% |

| 华邦电子 | 15.80 | TWD | +2.60% |

| 主控厂商 |

| 群联电子 | 454.0 | TWD | +4.25% |

| 慧荣科技 | 45.110 | USD | +2.38% |

| 联芸科技 | 40.80 | CNY | +0.62% |

| 点序 | 55.0 | TWD | +8.27% |

| 国科微 | 69.47 | CNY | +4.40% |

| 品牌/模组 |

| 江波龙 | 77.45 | CNY | +0.61% |

| 希捷科技 | 82.700 | USD | -0.41% |

| 宜鼎国际 | 237.0 | TWD | +1.07% |

| 创见资讯 | 103.0 | TWD | -1.44% |

| 威刚科技 | 82.6 | TWD | +2.23% |

| 世迈科技 | 17.230 | USD | +1.35% |

| 朗科科技 | 23.96 | CNY | +1.48% |

| 佰维存储 | 61.42 | CNY | +1.62% |

| 德明利 | 128.10 | CNY | +0.56% |

| 大为股份 | 13.81 | CNY | 0.00% |

| 封测厂商 |

| 华泰电子 | 30.95 | TWD | -0.80% |

| 力成 | 111.5 | TWD | -2.19% |

| 长电科技 | 33.00 | CNY | +0.58% |

| 日月光 | 137.5 | TWD | +3.77% |

| 通富微电 | 25.43 | CNY | +0.91% |

| 华天科技 | 9.84 | CNY | +0.72% |

深圳市闪存市场资讯有限公司 客服邮箱:Service@ChinaFlashMarket.com

CFM闪存市场(ChinaFlashMarket) 版权所有 Copyright©2008-2023 粤ICP备08133127号-2