DRAM也将走向3D堆叠?传SK海力士获DBI Ultra 3D互连技术的转让

编辑:Mavis 发布:2020-02-21 12:42据外媒报道,SK海力士已经与Xperi Corp旗下子公司Invensas签订新的专利与技术授权协议。该协议内容为SK海力士将获得Xperi广泛的半导体知识产权以及Invensas DBI Ultra 3D互连技术的转让。

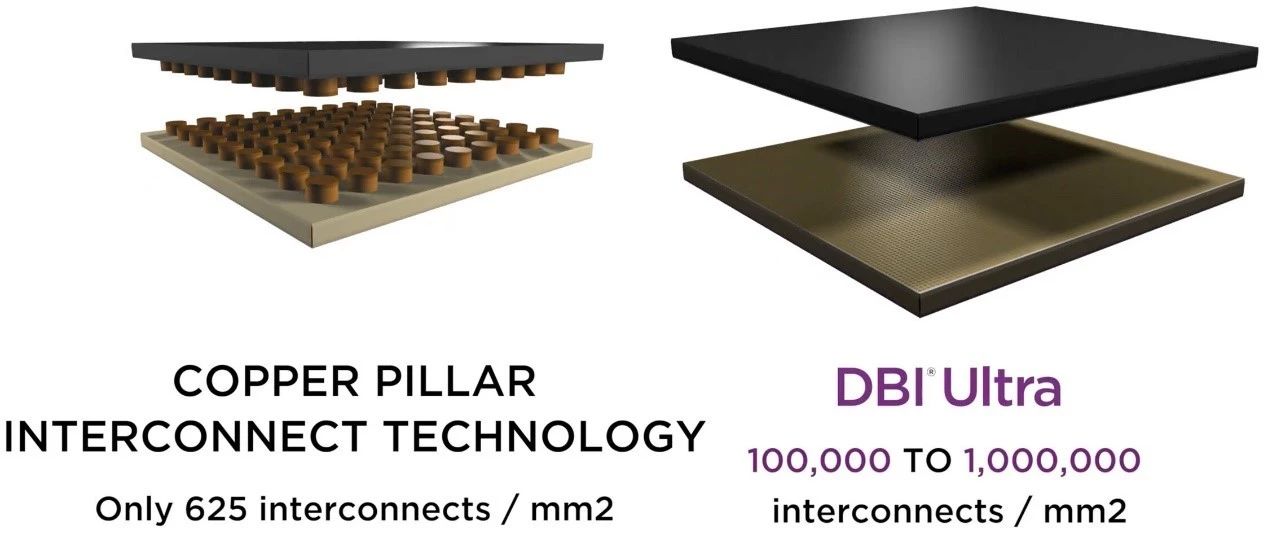

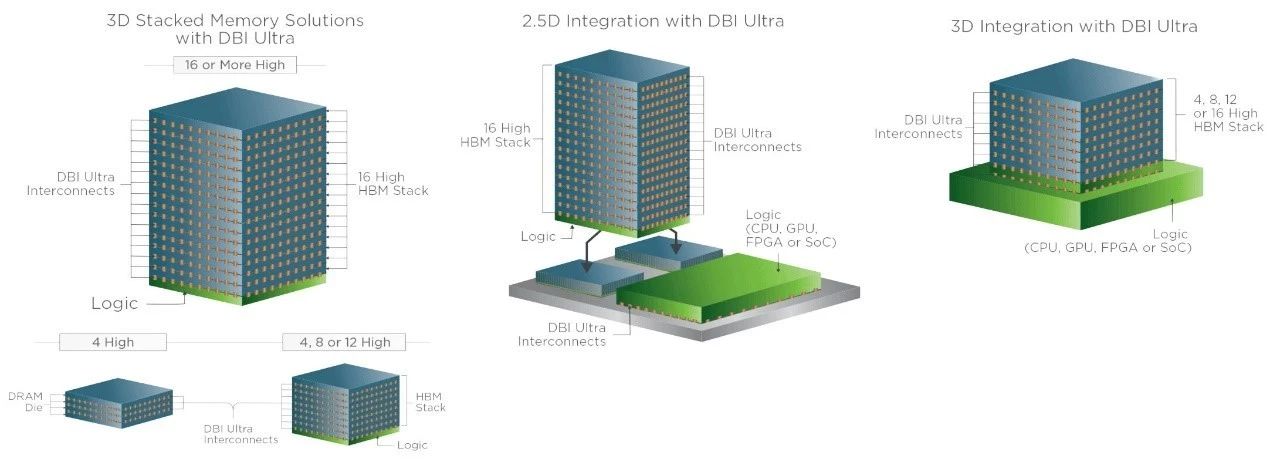

报道称,DBI Ultra 3D互连技术是die-to-wafer混合互联技术,可以制造8、12甚至16层高的芯片堆叠,满足下一代高性能计算对封装高度和性能的苛刻要求。此外,它还将开拓同质和异质3D封装的先河,有可能带领半导体行业超越摩尔定律,实现高灵活性的2.5D和3D封装。

Xperi Corporation的全资子公司Invensas总裁Craig Mitchell表示,我们很高兴与世界领先的存储解决方案制造商SK海力士保持长期合作关系。目前,半导体行业逐渐超越常规节点规模,转向混合键合,Invensas一直是该领域的领导者,致力于改进产品性能,功率并降低成本,我们很荣幸与SK海力士合作进一步开发和商业化我们的DBI Ultra技术,并期待利用这一革命性技术推出更好的内存解决方案。

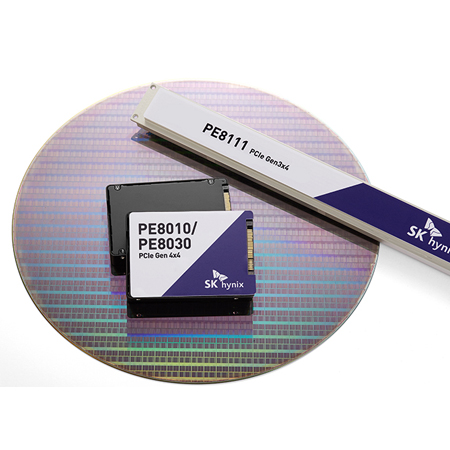

与其他下一代互连技术类似,DBI Ultra还能集成不同尺寸、不同工艺制程的IP模块,因此不但可用来制造DRAM、3DS、HBM等内存芯片,也可用于高集成度的CPU、GPU、ASIC、FPGA、SoC。SK海力士并未透露具体应用方向。

DBI Ultra 3D互连技术具体应用领域未知,内存不失为选择之一

SK海力士是全球领先的存储厂商,根据中国闪存市场数据,2019年SK海力士在DRAM市场排名第二,市占率29%,在NAND Flash市场与英特尔并列第五,市占率10%。而NAND Flash早已在2015年已经步入3D堆叠,现在已经开始向100+层堆叠过渡,但DRAM市场仍滞留在18nm-15nm工艺区间,不断逼近 10nm物理极限,但是仍未突破。

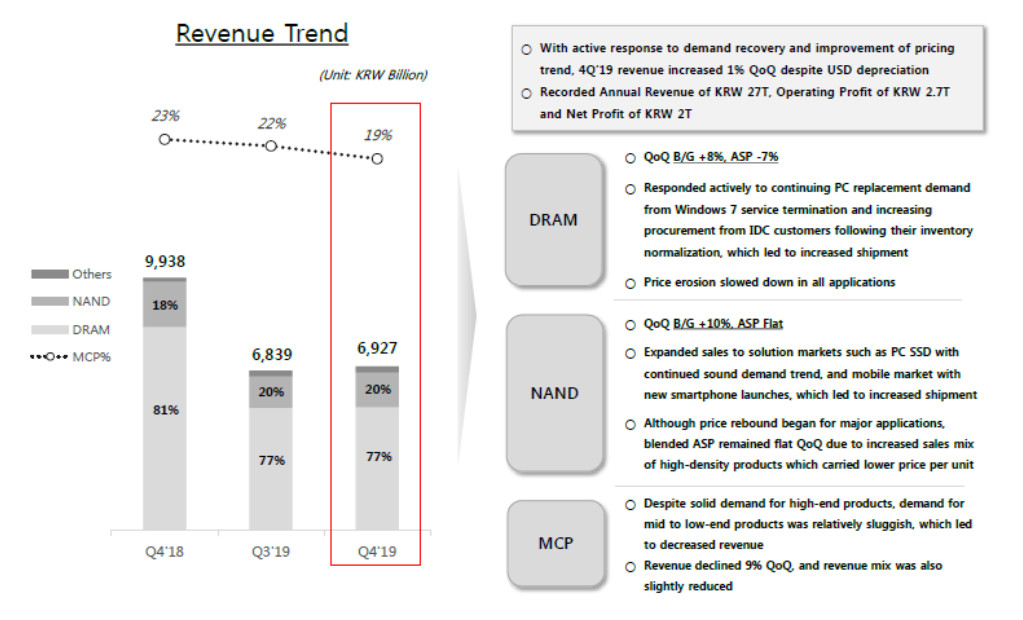

对于SK海力士而言,DRAM也是至关重要的一环,据SK海力士截至2019年12月31日的第四季度财报,DRAM业务营收占其总营收的77%,重要程度不言而喻。加之,SK海力士2019年第四季度净亏损 1180亿韩元,是自2012年Q2以来首度亏损,营业利润也较上一季度下降了50%。SK海力士也表示,由于产品线的利润率相对较低,再加上新技术过渡成本增加的负担,使得该季度亏损严重。因此,在巨大的盈利压力下,SK海力士试图通过引用新技术提升在行业内的技术优势也是无可厚非。

虽然目前SK海力士并未公开DBI Ultra 3D互连技术的具体应用领域,但鉴于DRAM市场目前的发展状况,以及DRAM对SK海力士整体发展的重要性,内存无疑是该技术的最佳应用选择之一。

DRAM缩放之路困难重重,EUV非根治良药,3D堆叠不失为一种选择

随着DRAM工艺不断微缩逼近10nm物理极限,光刻及蚀刻工艺所需的光罩数量不断提高,图案的分辨率很难得到保证,因此各大原厂纷纷有意引入分辨率更高的EUV光刻机推动DRAM持续发展。

其中三星在2019年3月开发出第三代10nm级(1Znm)工艺DRAM,传已在制造中整合了EUV极紫外光刻技术。SK海力士正在新工厂内建置EUV设备,下半年可完工,并评估导入EUV量产1anm级DRAM的时间。

美光科技在2019年不仅已开始大规模生产1Znm 16Gb DDR4产品,1Znm DDR5产品也已经送样。根据美光DRAM技术规划,下一代微细化工艺技术被命名为1α,1β和1γnm。据韩国媒体称,美光推迟了EUV的导入,可能推迟至1γnm技术之后,时间表暂不确定。

EUV技术光波长仅为13.5nm,比ArF(193 nm)短14倍,因此能够将图案分辨率降低到10nm以下。但是EUV工艺及其复杂,成本也十分昂贵,想要导入量产也并非易事。目前也仅有台积电和三星成功将EUV导入逻辑芯片的制造工艺中。

对于下一代内存设备的研发,方向有很多,但是均处于探索阶段。然而,毋庸置疑的是人们对高容量、高性能存储设备需求的不断增长。在NAND Flash成功实现3D堆叠之后,3D堆叠能否为DRAM发展开辟一条新路径,仍需市场检验。