随着5G逐步推广,我们的想象边际将被不断扩大,物联网、车联网、人工智能等领域将得到快速发展和普及,我们的生活也将被数字和运算包围,存储产业的发展将迎来新契机。IDC预测,到2023年全球数据总量将从2018年的33ZB增加到103ZB,2025年将进一步提高到175ZB,年复合增长率将达到61%。

为了满足海量数据存储需求,除了存储介质的不断创新,纠错程序也扮演着日益重要的角色。在此背景下,中国闪存市场ChinaFlashMarket专访了纠错方案服务商Codelucida联合创始人兼首席执行官Shiva Planjery,探讨什么样的纠错技术更能满足未来大容量存储需求以及Codelucida如何配合存储产业的飞速发展?

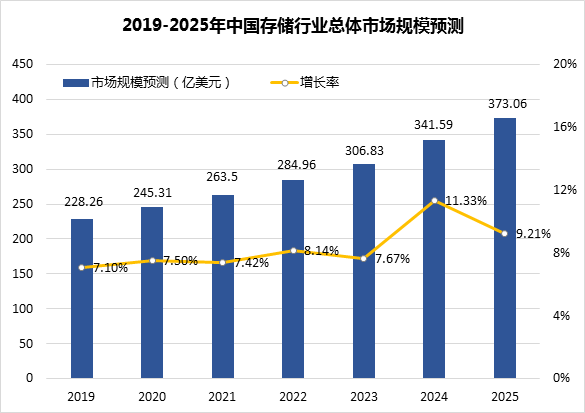

根据中国闪存市场ChinaFlashMarket数据,2019年全球半导体存储市场规模将达1100亿美元,ZB级海量数据存储需求带动下,市场规模也必将呈快速增长。根据IDC预测,2019年到2025年中国存储行业总体市场规模将保持每年7%以上复合增长率。

数据来源: IDC

虽然存储市场发展前景光明可期,但前进的路上仍有很多挑战克服。根据IDC数据,2018年产生的33ZB数据量中仅有5ZB保存下来,预计2023年产生的103ZB数据量中将只有12ZB被保存,数据保存率仅11.65%。未来大数据时代,数据将像石油一样珍贵,是未来社会发展的基石,如此“低的数据保存率”需要存储产业链企业通力合作,打通存储领域的“任督二脉”。

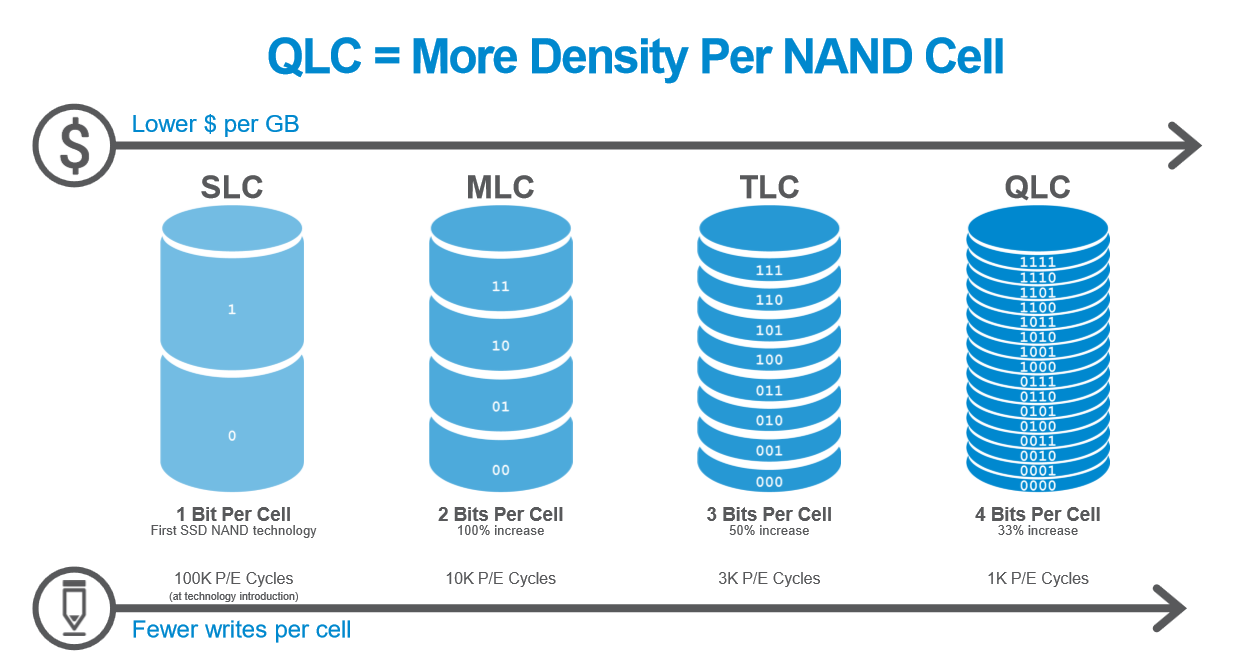

纵观全球六大核心原厂,到2019年,均已实现96层3D NAND量产,并向100+层3D NAND进军。另一方面,TLC 3D NAND Flash已经成为主流存储介质,西部数据、美光、铠侠(原东芝存储器)、英特尔均已经将TLC技术应用到企业级市场,QLC开始登上历史舞台。

近年来,3D NAND发展飞速,从2014年三星量产32层128Gb TLC闪存颗粒,到2019年全球六大核心原厂均实现96层3D NAND量产,且西部数据宣布正式量产出货96层QLC 3D NAND(单颗Die容量1.33Tb),单颗Die的容量已经增长超过10倍。

在高容量、低成本的市场需求驱动下,QLC逐渐成为消费类市场“新宠”。在近期西部数据召开的2019财年第四季度财务电话会议期间宣布已开始出货基于96层堆叠3D QLC闪存的产品,首批用于零售产品和移动SSD;市场消息,英特尔也已经开始产品策略转型,消费类产品将主推QLC+傲腾系列产品,TLC产品将主攻企业级市场;SK海力士也于今年5月份送样1Tb QLC NAND样品;三星在去年11月份发布了基于QLC技术的860 QVO SSD系列产品;美光也已经出货基于QLC NAND的SSD产品;铠侠(原东芝存储器)早在2017年就研发出96层QLC技术,并积极推进QLC的普及。

LDPC纠错加持下,TLC寿命“短板”逐步补齐,将大举进军企业级市场。NAND Flash从SLC发展到TLC、QLC,出错概率随着bit密度的增加而增大。自2014年三星发布全球首款面向企业级应用的TLC闪存固态硬盘“PM853T”之后,铠侠(原东芝存储器)英特尔、美光、SK海力士和西部数据相继推出企业级和数据中心市场应用的TLC固态硬盘。近日,西部数据更是推出新款企业级SSD UltraStar DCSS540,其寿命和可靠性更是被外媒赞为“坦克级”,耐久度最高可达10DWPD。

来源:中国闪存市场ChinaFlashMarket

TLC寿命的改善离不开纠错技术的发展。对于闪存技术如此飞速的发展,Shiva Planjery表示,“这是一个了不起的发展,主要由人工智能,物联网,大数据,数据分析等行业推动的更高容量存储需求的发展,是NAND闪存制造商通过研发创新技术得以实现的。但是随着技术的快速发展,堆叠层数的增加以及存储密度的增加,我们需要继续在所有支持技术上进行创新,以支持这种快速发展,这其中纠错技术起着举足轻重的作用,我们需要跟随着行业的发展继续创新。”

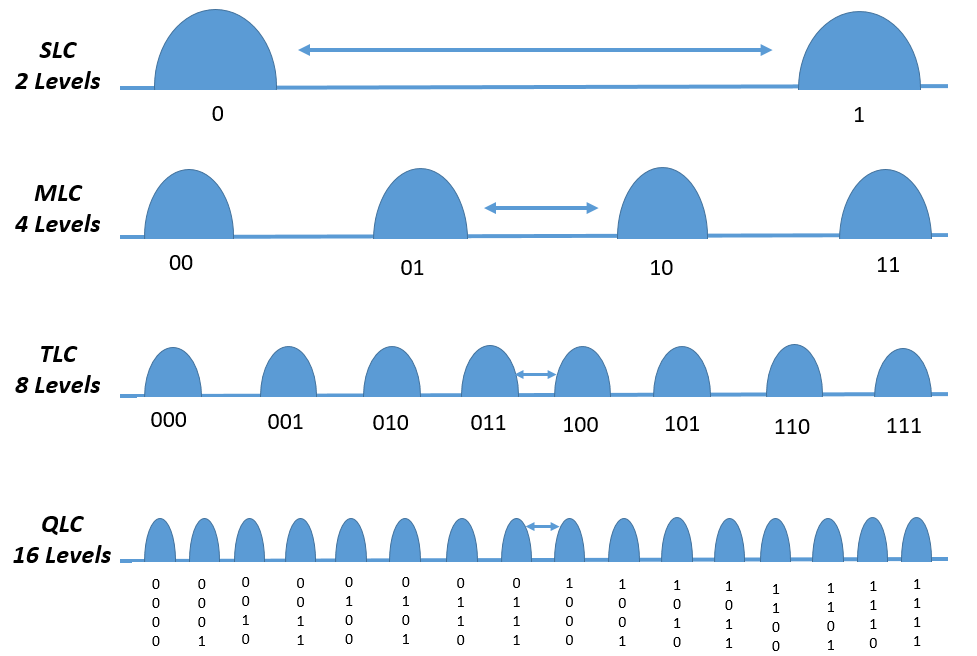

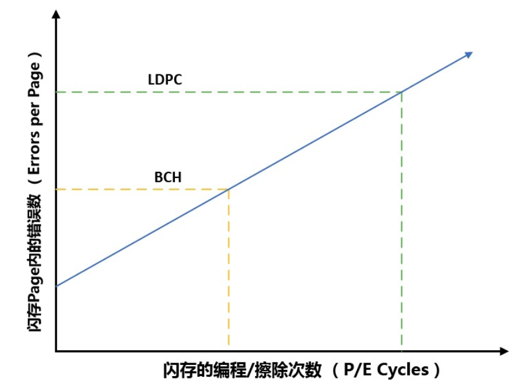

众所周知,QLC的P/E寿命仅为SLC的百分之一,随着每个cell里面电子数量的增多,擦写磨损、读写干扰、编程干扰影响会更加显著,当擦写次数增加时,内存中的氧化物层就会被破坏,使得捕获电子越来越困难,交叉概率增大。

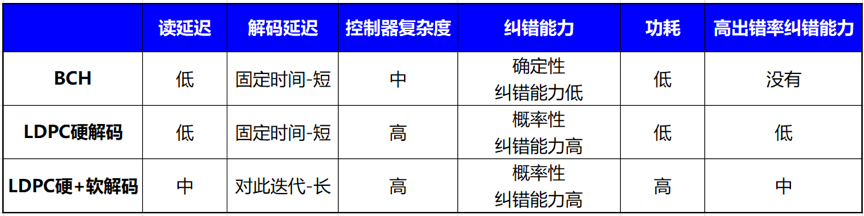

来源:美光

LDPC纠错最显著的优势是在NAND Flash每个Page中纠正更多的错误,减少NAND Flash无谓的写入损耗,所以低密度奇偶校验(LDPC)码纠错性能远高于BCH,这也让NAND Flash的使用寿命即P/E(可编程擦写)次数得到大幅的提升,从而增强TLC SSD的使用寿命和耐用性。

Shiva Planjery表示,“回顾早期的NAND闪存时,回到SLC闪存和MLC闪存,存储器本身不那么容易出错,它们是可靠的因此只需要简单的纠错方案。那时使用的纠错技术称为BCH的传统纠错。但是随着3D NAND堆叠层数的不断增加,且TLC和QLC技术的不断发展,简单的BCH纠错方案已经不能满足用户的需求了,人们需要功耗更低、性能更强的LDPC解决方案,以便控制器能够支持最新闪存技术的推广和应用,不仅现在是这样,未来随着层数和密度的不断增加,也同样是这样。”

存储技术的发展离不开纠错技术,Shiva Planjery表示,随着存储单元所容纳的Bit数量会越来越多,对算法的纠错能力要求也会越来越高,通过高效的纠错方案可以在一定程度上扩展NAND闪存的耐用性。不仅对当代存储,对于下一代存储产品来说也是一样重要,随着密度的不断提高,同时性能要求也随着从PCIE第3代到第4代,甚至是第5代的过渡而不断提高,纠错成为至关重要的组成部分,并将能够启用并支持所有最新一代的NAND闪存。”

Codelucida认为,传统的LDPC解决方案可能消耗大量功率以满足不断增长的吞吐量要求,并倾向于依赖复杂的错误恢复方案和复杂的介质管理策略。特别是对于采用FPGA实现的闪存控制器,传统的LDPC解决方案由于所需资源太大而无法满足低成本FPGA的所需吞吐量,这对于在FPGA中实现闪存控制器的供应商来说是一项艰巨的挑战。

对于大容量闪存芯片最佳的纠错解决方案,Shiva Planjery表示,适用于高密度存储的LDPC纠错解决方案除了需要满足最新NAND存储的耐用性和保持力要求,还需要具有高度可扩展性,以便能够在不要求过多功率和面积的情况下实现最高性能,满足高可靠性、高容量和低功耗,而该解决方案的答案是Codelucida的 FAID™ LDPC纠错技术。”

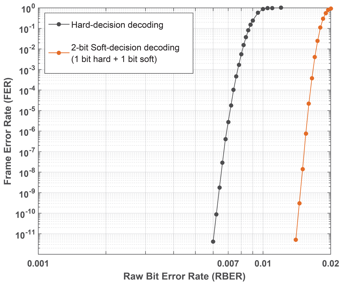

3D TLC纠错性能

来源:Codelucida

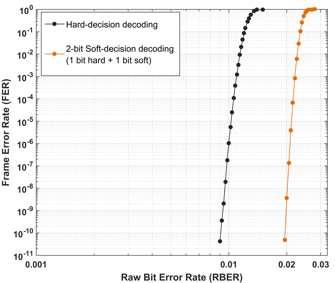

3D QLC纠错性能

来源:Codelucida

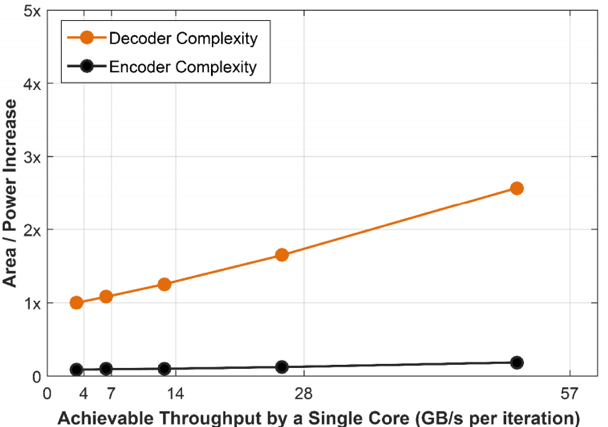

FAID™使用独特的专利编码和解码算法,这些算法本身更简单但在纠错能力方面更强,以满足闪存的极低错误率要求。由FAID™实现的译码器和编码器复杂度如下图。吞吐量可以增加10倍,译码器复杂度仅增加2倍。 即使对于更高的吞吐量,编码器复杂度仍保持相同,最多是译码器复杂度的 7%。

来源:Codelucida

Shiva Planjery解释道,“与主流LDPC相比,FAID™ LDPC纠错的主要区别在于算法。FAID™基于独特的编码和解码算法,这些算法是根据多年的研究开发的,与当今行业中使用的算法完全不同。它们本质上更简单,因此它们可以降低硬件复杂性,但却能够实现最强大的纠错能力。

与传统的LDPC解决方案相比,Codelucida的 FAID™的主要优势包括:

• 单个 IP 核(单核)实例可实现 10 倍的吞吐量增长;

• 功耗和资源使用至少减少 2 倍,特别是对于高吞吐量应用;

• 纠错能力增加 10%-15%,因此可得到原始误码率(RBER)的增加;

• 错误率降低四个数量级,大大降低了使用读取重试或软读取的频率,从而降低延迟提高了驱动器性能;

• 不使用LLR,这极大地简化了闪存控制器的管理;

• 无误码平层可实现闪存存储的极低错误率要求。

近年来,中国十分重视半导体产业的发展,也有一批优秀的厂商涌现出来。在存储领域,以长江存储和长鑫存储为代表,其中长江存储在今年9月份宣布量产基于Xtacking架构的64层3D NAND,长鑫存储DRAM产品亦进展顺利。

面对中国存储行业如此快速的发展,Shiva Planjery表示,“对中国存储行业的发展感到惊讶,如此多的支持和投资来全面开发本地制造的芯片和产品,从闪存控制器到SSD到存储芯片,DRAM芯片以及整体完整的存储系统。随着行业迅速发展包括性能和密度不断提高,高质量LDPC解决方案是必不可少的,这正是Codelucida的FAID™解决方案的用武之地。”

Codelucida独有的技术可支持这一行业的趋势,并且在支持中国市场的增长中发挥至关重要的作用。Shiva Planjery支持并对中国发展本地生态系统的5年战略计划感到惊讶,Codelucida也将发挥重要作用,已经积极与多个客户,中国的潜在客户,中国的合作伙伴,及其它生态系统中的成员发展成为伙伴关系,期待一起建立并发展中国的存储生态系统。

1、未经许可,任何人不能以任何形式转载、传输、重制、出版或播送;

2、如需转载或者引用,请注明来源:中国闪存市场。对内容若有异议,请与我们联系;

3、本专题版权归深圳市闪存市场资讯有限公司所有。

深圳市闪存市场资讯有限公司

Email:Service@Chinaflashmarket.com

地址:深圳市高新区中区科技中二路软件园一期4栋6楼